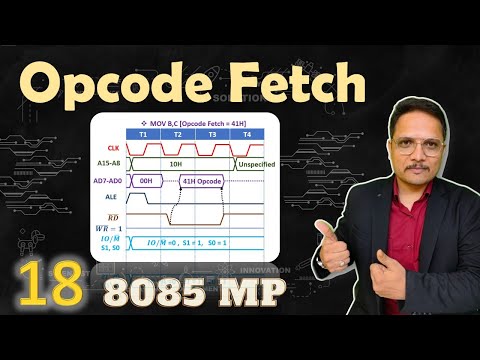

Answer : 235)How many and what are the machine cycles needed for execution of MOV D, C? Answer : 236)Which of the following register pairs can be directly stored in memory?

Q. How many machine cycle is needed for MOV BC?

Summary − So this instruction MOV M, E requires 1-Byte, 2-Machine Cycles (Opcode Fetch, Memory Read) and 7 T-States for execution as shown in the timing diagram.

Table of Contents

- Q. How many machine cycle is needed for MOV BC?

- Q. How many machine cycles are required for in instruction?

- Q. How many T states are required for execution of MOV BC?

- Q. What type of instruction is mov?

- Q. What does the MOV instruction do?

- Q. Which mode the Cpsr Cannot be written?

- Q. What is the difference between LDR and LDRB?

- Q. What is ARM LDRB?

- Q. What does the B mean in LDRB or what is the difference between LDR and LDRB in arm?

- Q. What does CMP do in arm?

Q. How many machine cycles are required for in instruction?

In 8085 microprocessor, we have conditional jump instructions. If condition is not met, it requires 2 machines cycles to execute the instruction.

Q. How many T states are required for execution of MOV BC?

Only opcode fetching is required for this instruction and thus we need 4 T states for the timing diagram.

Q. What type of instruction is mov?

It occupies only 1-Byte in memory. MOV E, M is an example instruction of this type. It is a 1-Byte instruction….Instruction type MOV r, M in 8085 Microprocessor.

| Mnemonics, Operand | Opcode | Bytes |

|---|---|---|

| MOV H, M | 66 | 1 |

| MOV L, M | 6E | 1 |

Q. What does the MOV instruction do?

The mov instruction copies the data item referred to by its second operand (i.e. register contents, memory contents, or a constant value) into the location referred to by its first operand (i.e. a register or memory).

Q. Which mode the Cpsr Cannot be written?

Since the CPSR cannot be modified in user mode, software must change to supervisor mode to get write access (supervisor mode can be entered by executing the SVC instruction, or by certain exceptions).

Q. What is the difference between LDR and LDRB?

The difference arises from the selection of “unsigned char” vs “unsigned in” in C. My understanding is that LDRB does a zero-extend which the LDR does not.

Q. What is ARM LDRB?

Description. The LDRB instruction loads a byte from addr_mode into dest . This byte is zero-extended into a 32-bit word enabling 8-bit memory data to be manipulated. It also enables PC-relative addressing if used as a base register. The condition needs to be a valid value; else the instruction is rendered an NOP.

Q. What does the B mean in LDRB or what is the difference between LDR and LDRB in arm?

Little Endian Format means the least significant byte is stored in the lower memory address. LDR makes r0 = the string. LDRB loads the least significant byte held in r0, into r2 offset by 1 bit. <- 0000 0017 (ascii for q) or <- 0000 006D (ascii for m).

Q. What does CMP do in arm?

The CMP instruction subtracts the value of Operand2 from the value in Rn . This is the same as a SUBS instruction, except that the result is discarded. The CMN instruction adds the value of Operand2 to the value in Rn .